Микроэлектроника проникла практически всюду — от бытовых приборов до спутников и систем вооружения. Современные технологии позволяют на базе одного чипа реализовывать все более сложные вычислительные системы, и к их надежности предъявляются все более высокие требования. Надежность же подразумевает механизмы, обеспечивающие устойчивость к сбоям и отказам. Ключевой задачей становится тестирование таких механизмов на ранних стадиях разработки микросхем.

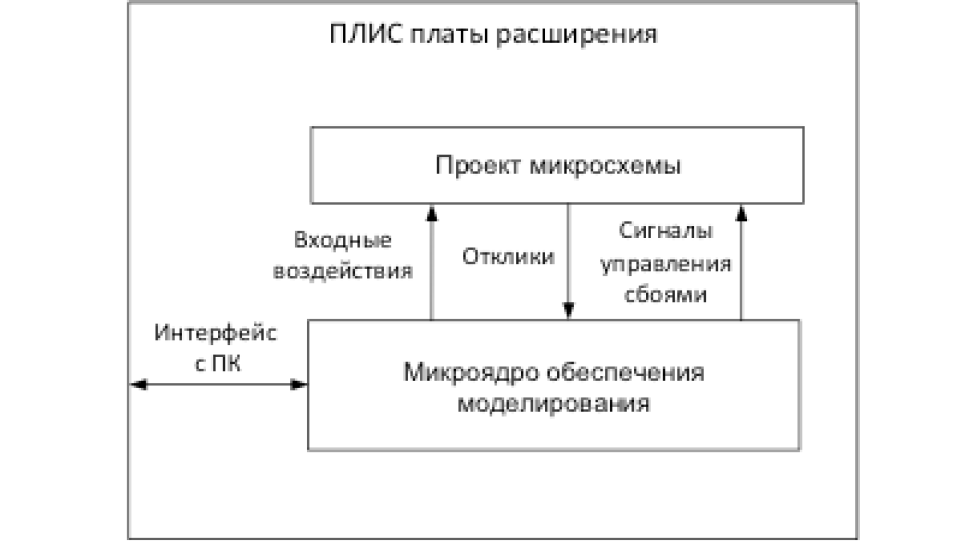

Содержимое ПЛИС (программируемой логической интегральной схемы) платы расширения

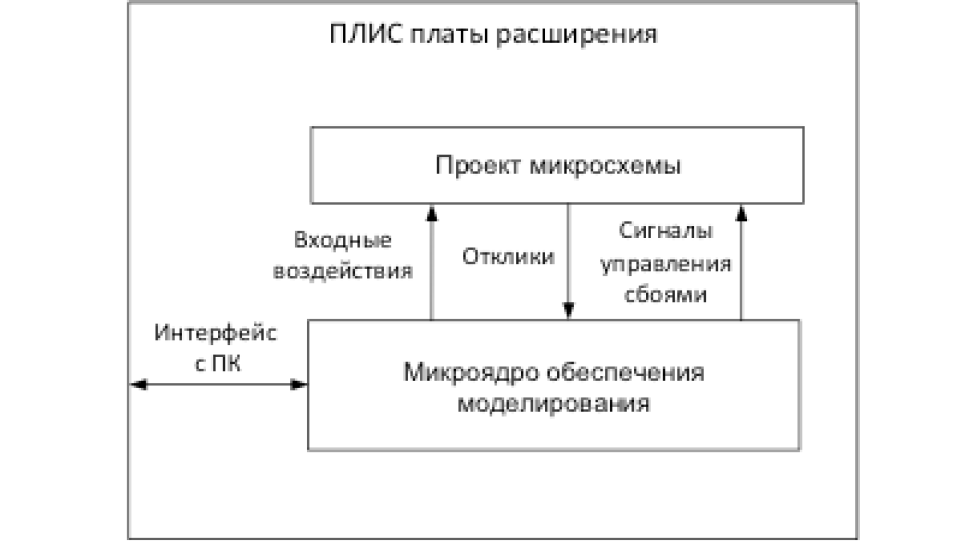

Содержимое ПЛИС (программируемой логической интегральной схемы) платы расширения

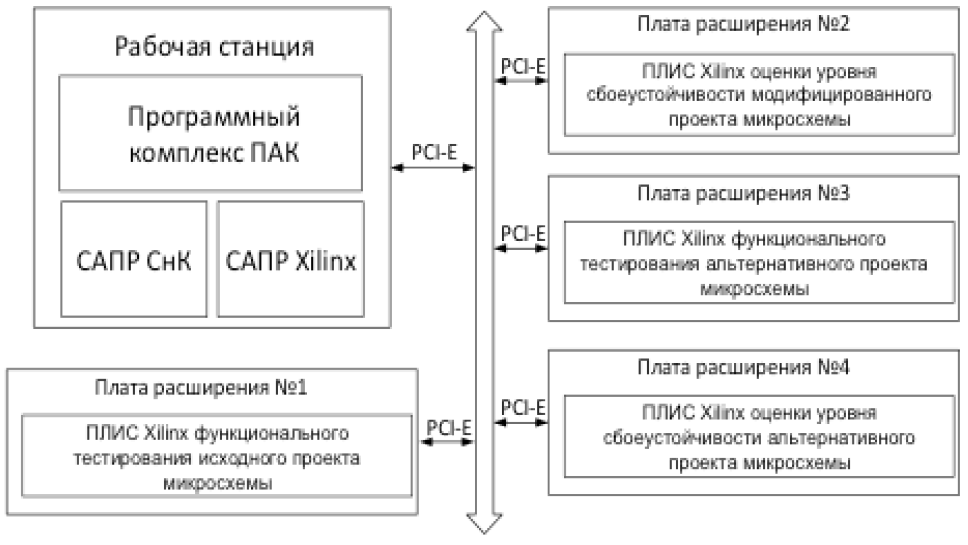

Структурная схема программно-аппаратного комплекса

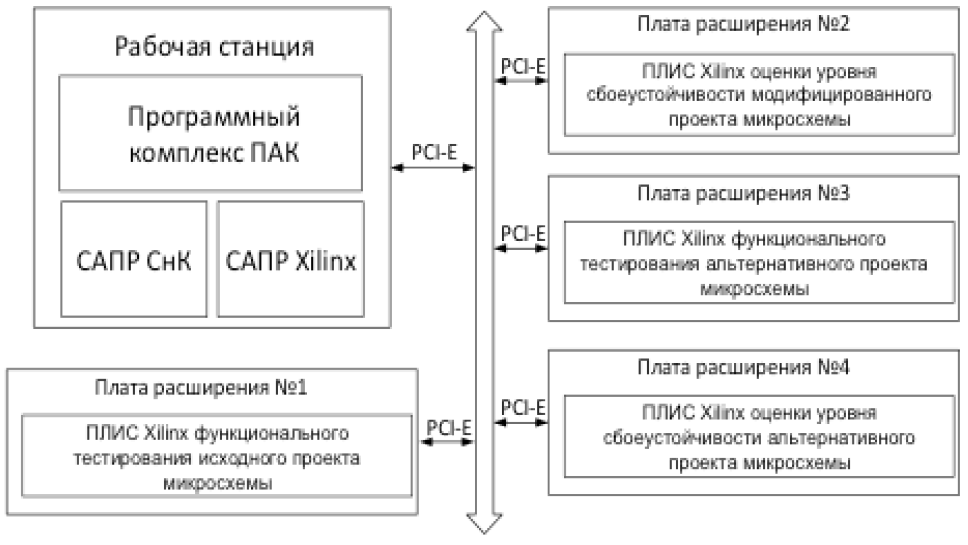

Структурная схема программно-аппаратного комплекса

Необходимы механизмы, обеспечивающие устойчивость микросхемы к сбоям и отказам. Ключевой задачей становится тестирование таких механизмов на ранних стадиях разработки

Ускорение тестирования сбоеустойчивых сложных вычислительных систем на базе одного чипа (так называемых систем на кристалле, СнК) подразумевает решение целого комплекса взаимосвязанных задач. Сюда входят выбор метода и технологии тестирования, ускорение тестирования основной функциональности системы, разработка моделей возникновения неисправностей и ускорение оценки эффективности механизмов сбоеустойчивости.

При этом выбранная технология тестирования должна быть внедрена в маршрут разработки целевых микросхем, который обычно осуществляется с помощью системы автоматизированного проектирования (САПР). Стандартный маршрут проектирования включает следующие этапы: написание модели разрабатываемой системы на языках описания аппаратуры (Verilog, "1364-2005 — IEEE Standard for Verilog Hardware Description Language"; SystemVerilog, "1800-2012 --- IEEE Standard for SystemVerilog — Unified Hardware Design, Specification and Verification Language"), разработка программных тестов и проведение на их основе функционального тестирования полученной модели, синтез логической схемы устройства в базисе целевой микросхемы (в формате Verilog netlist), функциональное тестирование полученного описания микросхемы с учетом временных задержек распространения сигналов, размещение и трассировка элементов логической схемы и проведение посттрассировочного функционального тестирования, генерация технологических данных для производства. При обнаружении функциональных несоответствий на одном из этапов тестирования осуществляется цикл перепроектирования, подразумевающий возврат к предыдущим этапам.

Известные САПР микросхем осуществляют тестирование разрабатываемых СнК преимущественно программными методами, что приводит к значительным временным затратам. При этом в большинстве САПР отсутствует встроенная возможность оценки сбоеустойчивости разрабатываемых СнК. Поэтому необходимо создавать программно-аппаратные решения для тестирования и оценки сбоеустойчивости разрабатываемых микросхем. Причем для СнК аэрокосмического применения важно учитывать специфику условий их эксплуатации. Основной источник неисправностей в микросхемах, применяемых в авионике и космических системах,— космическая радиация (E. Petersen, Single Event Effects in Aerospace, IEEE Press, 2011). Воздействие заряженных частиц галактических космических лучей, естественных радиационных поясов Земли, а также солнечных космических лучей на микросхему может приводить к возникновению временных сбоев или постоянных отказов в работе (М. И. Панасюк и Л. С. Новиков, Модель космоса. Том II. Воздействие космической среды на материалы и оборудование космических аппаратов, Москва, 2007). Эффекты от воздействия радиации можно разделить на две группы (K. Iniewski, Radiation Effects in semiconductors, CRC Press, 2010): эффекты поглощенной дозы и одиночные случайные эффекты.

Первая группа характеризует постепенную деградацию физических свойств вещества микросхемы в результате воздействия множества частиц космической радиации и описывается такими интегральными показателями, как поглощенная доза (выделенная потоком частиц энергия в единице массы вещества за время полета космического аппарата). Основные методы борьбы с эффектами этой группы — технологические, позволяющие в результате использования новых материалов и технологии снизить чувствительность микросхемы к эффектам поглощенной дозы.

Борьба со случайными одиночными эффектами требует дополнительных усилий, в том числе внедрения в схему устройства средств обеспечения сбоеустойчивости. Причина в том, что чисто технологические методы борьбы пока не позволяют снизить частоту возникновения таких неисправностей до уровня, не угрожающего работоспособности микросхемы. Одиночные эффекты, в отличие от эффектов накопленной дозы, имеют случайный характер и возникают вследствие попадания в микросхему отдельных тяжелых заряженных частиц. Основными типами таких эффектов являются инверсия логического значения элемента памяти (триггера) (Single Event Upset, SEU), залипание триггера в состоянии логического нуля или единицы (Stuck_at_0/1), а также паразитные импульсы напряжения в комбинационной логике (Single Event Transient, SET).

При тестировании сбоеустойчивости СнК аэрокосмического применения по отношению к случайным одиночным эффектам широко используется метод внедрения неисправностей (H. Ziade, R. Ayoubi и R. Velazco, "A Survey on Fault Injection Techniques", The International Arab Journal of Information Technology, 1, 171, 2004). Идея метода заключается в имитации возникновения радиационных сбоев и отказов и оценке их влияния. При реализации метода важно обеспечить как высокую скорость тестирования (характерную для аппаратных методов внедрения неисправностей), так и высокую информативность и повторяемость экспериментов (они присущи программным методам). Поэтому тестирование на основе метода внедрения неисправностей проводится с использованием комбинированных, программно-аппаратных решений.

В результате проведения исследований в Московском авиационном институте (национальном исследовательском университете) в рамках федеральной целевой программы "Исследования и разработки по приоритетным направлениям развития научно-технологического комплекса России на 2014-2020 годы" было предложено решение данной задачи для СнК аэрокосмического применения. Разработан экспериментальный образец программно-аппаратного комплекса (ПАК), способного выполнять контроль сбоеустойчивости проекта микросхемы СнК. Комплекс основан на ПЛИС-прототипировании и расширенном методе внедрения неисправностей (ПЛИС — программируемая логическая интегральная схема, O. Brekhov, K. Kordover, A. Klimenko и M. Ratnikov, "FPGA-Prototyping with Advanced Fault Injection Methodology for Tolerant Computing Systems Simulation", DCCN 2015, Moscow, 2016). В состав комплекса входят персональный компьютер на базе процессора Intel Xeon и PCI-платы расширения на базе ПЛИС Xilinx Virtex-6 (PCI — Peripheral component interconnect, шины ввода--вывода).

ПАК реализует пошаговую методику моделирования проектов микросхем с имитацией сбоев (первоначально методика предложена в (8)). Методика позволяет осуществлять функциональное тестирование, а также оценку эффективности механизмов обеспечения сбоеустойчивости проекта СнК, представленного в формате Verilog netlist, на основе результатов моделирования работоспособности его ПЛИС-прототипа в условиях наличия и отсутствия неисправностей.

Идея метода — в имитации возникновения радиационных сбоев и отказов и дальнейшей оценке их влияния

Внешний вид экспериментального образца программно-аппаратного комплекса

Фото: Александр Клименко

В заключение отметим, что создание новых высокопроизводительных средств тестирования сбоеустойчивых СнК, подобных представленному ПАК, крайне необходимо для дальнейшего развития отечественной микроэлектроники. Сокращение сроков проектирования и снижение стоимости работ позволят отечественным разработкам получить конкурентное преимущество, как на внутреннем, так и на международных рынках, что будет способствовать популяризации отечественной микроэлектронной продукции и реализации политики импортозамещения.